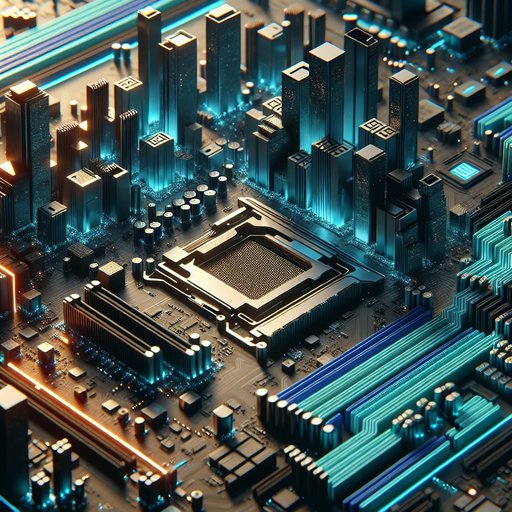

Moderne moederborden zijn geëvolueerd van simpele hostplatforms naar compacte, razendsnelle backplanes die op een stille manier tegenstrijdige eisen met elkaar in balans brengen: steeds snellere I/O zoals PCIe 5.0, toenemende piek stroomvereisten van CPU's en GPU's, en de noodzaak om te integreren en samen te werken met een heleboel standaardcomponenten. Deze ontwikkeling weerspiegelt tientallen jaren van opgebouwde engineeringdiscipline op het gebied van signaalintegriteit, energievoorziening, firmware en mechanisch ontwerp. Als je bekijkt hoe borden vandaag de dag zo complex zijn geworden, begrijp je waarom de formaten bekend lijken, terwijl de onderliggende technologie weinig weg heeft van de ATX-ontwerpen uit de jaren '90, en waarom geleidelijke gebruiksvriendelijke functies de ingrijpende architectonische veranderingen onder de koellichamen en omhulsels verhullen.

Moederborden staan centraal in de evolutie van computers, omdat ze de roadmap van halfgeleiders omzetten in bruikbare systemen. Naarmate processors meer functies integreerden en de I/O-snelheden stegen, namen bordontwerpers de rol aan van ingenieurs voor hogesnelheidverbindingen, niet alleen van componenten. Het resultaat is dat een modern ATX-bord in wezen een gecontroleerd-impedantie backplane is, met strikte eisen voor timing, verlies en crosstalk. Deze verschuiving bepaalt welke functies op een platform beschikbaar zijn, hoeveel uitbreidingsapparaten het kan ondersteunen op volle snelheid en hoe lang het compatibel kan blijven naarmate de standaarden zich ontwikkelen.

PCI Express is een goed voorbeeld van deze uitdaging. De overstap van PCIe 3.0 met 8 GT/s naar 4.0 met 16 GT/s en nu 5.0 met 32 GT/s halveert de kanaalverliesmarge bij elke stap, wat een strikte indeling van multi-gigahertz lay-outs vereist. Ontwerpers gebruiken low-loss dielectrica, dikkere koperdraden, nauwkeurige differentiële paarmatching en zorgvuldige via-ontwerpen om de insertieverlies binnen de specificaties te houden, en ze zetten redrivers of retimers in op lange paden, vooral voor de M.2-sloten aan de voorkant en achterzijde. Lane bifurcatie en switch-chips verdelen de beperkte CPU-lanes tussen x16 graphics, x4 NVMe en chipset uplinks, terwijl gelijkstelling en distributie van referentiekronkels stabiel moeten blijven over elke topologie die de BIOS blootlegt.

Platformcontrollers, zoals Intel's PCH via DMI en AMD's chipsetverbindingen over PCIe, verdelen de bandbreedte verder, waardoor lane-budgettering een belangrijke ontwerpoefening op bordniveau wordt. De stroomvoorziening is even agressief gevorderd. Moderne CPU's kunnen van lage idle naar turbo-stromen schakelen in microseconden, dus borden gebruiken multi-fase VRM's met slimme voedingsstadia, hoge-stroom inductoren en snelle transiënte responsafstemming. ATX 3.0 en 3.1 introduceerden nieuwe verwachtingen voor PSU bij GPU-lasten en introduceerden de 16-pins 12VHPWR, die in de bijgewerkte richtlijnen is vervangen door 12V-2x6, terwijl de PCIe-slot van het moederbord nog steeds tot 75 W levert onder de CEM-specificatie.

Load-line calibratie, temperatuurbewuste stroombalancering en aanzienlijke heatsinking houden VRM's binnen de limieten tijdens langdurige boosts. Aan de geheugenzijde heeft DDR5 aanzienlijke regulatie naar de DIMM verplaatst via een onboard PMIC, wat de manier waarop borden stroom voor geheugenchannels routeren en filteren, heeft veranderd. Geheugen-signalisatie illustreert de integratietrad-offs. Elke DDR-generatie heeft de timing- en integriteitsvensters verscherpt, waardoor borden worden aangemoedigd naar topologieën en sporenlengtes die minder DIMMs per kanaal bevorderen voor hogere snelheid.

DDR5 voegt on-die ECC toe voor array-betrouwbaarheid en vereist per-DIMM training beheerd door firmware, terwijl de PMIC op de module de complexiteit van regulatie aan de bordzijde vermindert maar de coördinatie tussen SPD-gegevens, BIOS-geheugentraining en stroomsequenties verhoogt. Fabrikanten publiceren QVL-lijsten nadat ze specifieke DIMM-configuraties hebben gevalideerd, omdat kleine wijzigingen in sporenlengte, via-stubs en socketplaatsing kunnen bepalen of geadverteerde snelheden haalbaar zijn. Overclockingprofielen zoals XMP en EXPO bestaan binnen deze beperkingen, en serverplatforms ruilen piekfrequentie in voor meer kanalen en capaciteit. De I/O-mix is een puzzel van overlappende standaarden geworden.

USB4 en Thunderbolt vereisen Type‑C retimers, USB‑PD controllers, firmware-gebeheerde alternatieve modi, en zorgvuldige EMI-controle om samen te kunnen bestaan met Wi‑Fi en Bluetooth-radio's op hetzelfde bord. DisplayPort Alt Mode deelt pinnen met high-speed USB, terwijl PCIe tunneling over USB4 routingbeslissingen toevoegt die de native PCIe-lanes die voor NVMe zijn gereserveerd, niet mogen uithongeren. Netwerken varieert van geïntegreerde 2.5 GbE PHY's tot 10 GbE-controllers met eigen SerDes en thermische behoeften, plus M.2 Key‑E-sockets voor Wi‑Fi-modules die antennes delen met Bluetooth. Audio-codecs, front-panel USB 3.2 Gen2x2 headers en legacy SATA strijden allemaal om bordruimte en signaalpaden zonder de compliance-marges of radiated emissions-limieten te overschrijden.

Mechanisch en thermisch ontwerp zijn samen met elektronica geëvolueerd om alles betrouwbaar te houden. Hogere VRM-stromen hebben de overstap naar grote koellichaam met vinnen, heatpipes en soms backplates gedreven om warmte weg te verspreiden van de voedingsstadia rond de CPU-socket. PCIe 5.0 M.2-sloten introduceren strakke bochten en langere runs die vaak retimers vereisen, en de resulterende SSD's worden vaak geleverd met aanzienlijke koellichamen of zelfs kleine ventilatoren, die borden moeten kunnen accommoderen zonder in de weg te zitten van GPU-koelers. Vormfactoren zoals ATX, microATX en Mini‑ITX beperken het aantal lagen, de spatiëring van slots en de keep-out zones; serverborden in SSI‑CEB of EEB-formaten bieden meer lagen en sporen voor multi-socket of high-channel geheugentopologieën.

De externe uitstraling—RGB-beschermkappen en decoratieve schilden—verbergt een functioneel doel: gecontroleerde luchtstroom en afscherming voor dichte high-speed gebieden. Firmware is de orkestrator geworden die ervoor zorgt dat heterogene standaarden coherent functioneren. UEFI heeft de legacy BIOS vervangen, waardoor complexe initialisatie voor PCIe-gelijkstelling, DDR5-training, USB4-beleid en beveiligingsfuncties zoals Secure Boot en TPM 2.0 of firmware TPM mogelijk is. Platformmicrocode en leverancierframeworks, zoals AMD's AGESA en Intel's referentiecode, leveren voortdurende verbeteringen in geheugcompatibiliteit, boostgedrag en apparaatsenumeratie, waardoor de bruikbare levensduur van een bord wordt verlengd over CPU- en randapparatuurvernieuwingen.

Enthousiastelingenopties zoals PCIe-lane bifurcatie, Resizable BAR en ASPM-afstemming brengen de afwegingen tussen prestaties, compatibiliteit en stroomverbruik aan het licht. In servers voegt een speciale BMC met standaarden zoals IPMI en Redfish remote management, telemetrie en veldupdates toe, onafhankelijk van de host-CPU. De integratie over zoveel domeinen heeft nieuwe validatiepraktijken gedwongen. Borden ondergaan compliance-testing voor PCIe 5.0 eye-diagrammen en ontvanger marges, USB4-linktraining en interoperabiliteit, en DDR5-timing op geadverteerde snelheden, waarbij vaak firmware wordt iteratief om hoekgevallen op te lossen die zijn ontdekt met retailapparaten.

Electromagnetische compatibiliteit en coexistence-testing zorgen ervoor dat hogesnelheidslanen geen draadloze modules of gevoelige audiopaden overstijgen, terwijl thermische kamers en stroomtransiënte tests het gedrag onder de slechtste geval boosts verifiëren, gedefinieerd door modern CPU-stroombeheer. Gekwalificeerde leverancierslijsten, openbare BIOS-updates en duidelijke lane-maps in handleidingen zijn het zichtbare resultaat van dit werk, waardoor gebruikers afwegingen kunnen navigeren zoals het uitschakelen van SATA-poorten wanneer bepaalde M.2-sloten zijn bezet. Het moderne moederbord is daarom de stille ruggengraat die de ultramoderne signaling verzoent met pragmatische achterwaartse compatibiliteit. Het ondersteunt PCIe 5.0 bij 32 GT/s naast USB4-tunnels, voedt burstachtige multi-honderd watt lasten zonder droop, en biedt nog steeds headers voor oudere randapparatuur.

Naarmate PCIe 6.0 met PAM4-signalisatie en forward error correction de mainstream-platforms bereikt na de initiële serveradoptie, zullen borden hun signaalbudgetten verder aanscherpen en meer afhankelijk worden van retimers en low-loss materialen. Tegelijkertijd zal de voortdurende integratie van CPU's sommige functies van het bord afschuiven, maar de taak blijft hetzelfde: het toewijzen van eindige lanes, stroom en thermiek zodat verschillende standaarden naadloos aanvoelen voor de gebruiker.