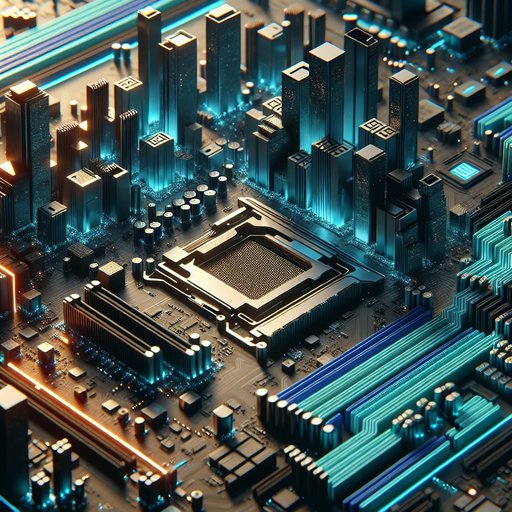

Las placas base modernas han evolucionado de simples plataformas de conexión a complejos backplanes de alta velocidad que manejan de manera silenciosa requisitos conflictivos: la necesidad de I/O cada vez más rápida como PCIe 5.0, las crecientes demandas de energía transitoria de CPUs y GPUs, y la integración y cooperación con una diversidad de estándares de componentes. Esta evolución refleja décadas de disciplina en ingeniería acumulada en áreas como la integridad de señales, la entrega de energía, el firmware y el diseño mecánico. Al analizar cómo las placas han alcanzado la complejidad actual, se entiende por qué los factores de forma pueden parecer familiares, mientras que la tecnología subyacente poco se asemeja a los diseños ATX de los años 90, y por qué las características incrementales orientadas al usuario ocultan cambios arquitectónicos significativos bajo los disipadores de calor y coberturas.

Las placas base están en el centro de la evolución de la computación porque traducen las hojas de ruta de los semiconductores en sistemas utilizables. A medida que los procesadores integraron más funciones y las velocidades de entrada/salida aumentaron, los diseñadores de placas asumieron el papel de ingenieros de interconexión de alta velocidad, no solo de organizadores de componentes. El resultado es que una placa ATX moderna es, en efecto, un plano de impedancia controlada con presupuestos estrictos de temporización, pérdida y diafonía. Este cambio determina qué características aparecen en una plataforma, cuántos dispositivos de expansión puede soportar a máxima velocidad y cuánto tiempo puede mantenerse compatible a medida que avanzan los estándares.

PCI Express ejemplifica este desafío. Pasar de 8 GT/s en PCIe 3.0 a 16 GT/s en 4.0 y ahora a 32 GT/s en 5.0 reduce a la mitad el margen de pérdida del canal en cada paso, lo que obliga a una disciplina de diseño a múltiples gigahercios. Los diseñadores utilizan dieléctricos de baja pérdida, cobre más grueso, emparejamiento diferencial ajustado y un diseño cuidadoso de vias para mantener la pérdida de inserción dentro de las especificaciones, y despliegan redriver o retimer en rutas largas, especialmente para los slots M.2 del panel frontal y trasero. La bifurcación de carriles y los chips de conmutación dirigen los carriles limitados de la CPU entre gráficos x16, NVMe x4 y enlaces de chipset, mientras que la ecualización y la distribución del reloj de referencia deben permanecer estables en cada topología que exponga la BIOS.

Los controladores de plataforma, como el PCH de Intel a través de DMI y los enlaces de chipset de AMD sobre PCIe, dividen aún más el ancho de banda, convirtiendo la planificación de carriles en un ejercicio central de diseño a nivel de placa. La entrega de energía avanzó con la misma agresividad. Los CPUs modernos pueden cambiar de corrientes de reposo bajo a turbo en microsegundos, por lo que las placas emplean VRMs de múltiples fases con etapas de potencia inteligentes, inductores de alta corriente y ajuste de respuesta transitoria rápida. ATX 3.0 y 3.1 trajeron nuevas expectativas de PSU para transitorios de carga de GPU e introdujeron el conector de 16 pines 12VHPWR, reemplazado en las guías actualizadas por el 12V-2x6, mientras que el slot PCIe de la placa base aún suministra hasta 75 W bajo la especificación CEM.

La calibración de la línea de carga, el balanceo de corriente consciente de la temperatura y un disipador de calor sustancial mantienen los VRMs dentro de los límites durante aumentos sostenidos. En el lado de la memoria, DDR5 trasladó una regulación significativa al DIMM a través de un PMIC integrado, reformulando la forma en que las placas dirigen y filtran la energía para los canales de memoria. La señalización de memoria ilustra los compromisos de integración. Cada generación de DDR ajustó los tiempos y las ventanas de integridad, llevando a las placas hacia topologías y longitudes de trazas que favorecen menos DIMMs por canal para una mayor velocidad.

DDR5 añade ECC en el chip para la fiabilidad del arreglo y requiere entrenamiento por DIMM gestionado por firmware, mientras que el PMIC en el módulo reduce la complejidad de regulación del lado de la placa, pero aumenta la coordinación entre los datos SPD, el entrenamiento de memoria de la BIOS y la secuenciación de potencia. Los fabricantes publican listas QVL tras validar configuraciones específicas de DIMM porque cambios minúsculos en la longitud de las trazas, las vias y la colocación de los sockets pueden decidir si las velocidades anunciadas son alcanzables. Los perfiles de overclocking como XMP y EXPO existen dentro de estas limitaciones, y las plataformas de servidor intercambian frecuencia máxima por más canales y capacidad. La mezcla de I/O se ha convertido en un rompecabezas de estándares superpuestos.

USB4 y Thunderbolt requieren retimers Type-C, controladores USB-PD, modos alternativos gestionados por firmware y un cuidadoso control de EMI para coexistir con radios Wi-Fi y Bluetooth en la misma placa. El modo alternativo DisplayPort comparte pines con USB de alta velocidad, mientras que el túnel PCIe sobre USB4 añade decisiones de enrutamiento que no deben privar a los carriles PCIe nativos reservados para NVMe. La red varía desde PHYs integrados de 2.5 GbE hasta controladores de 10 GbE con sus propias necesidades térmicas y de SerDes, además de sockets M.2 Key-E para módulos Wi-Fi que comparten antenas con Bluetooth. Los códecs de audio, los encabezados USB 3.2 Gen2x2 del panel frontal y el SATA heredado compiten por espacio en la placa y caminos de señal sin violar márgenes de cumplimiento o límites de emisiones radiadas.

El diseño mecánico y térmico evolucionó junto con la electrónica para mantener todo fiable. Las corrientes más altas en los VRMs impulsaron el uso de disipadores de calor grandes, tubos de calor y, a veces, placas traseras para dispersar el calor lejos de las etapas de potencia agrupadas alrededor del zócalo del CPU. Los slots M.2 PCIe 5.0 introducen curvas ajustadas y recorridos más largos que a menudo requieren retimers, y los SSD resultantes tienden a enviarse con disipadores de calor sustanciales o incluso pequeños ventiladores, que las placas deben acomodar sin chocar con los refrigeradores de GPU. Los factores de forma como ATX, microATX y Mini-ITX restringen la cantidad de capas, el espacio entre slots y las zonas de exclusión; las placas de servidor en formatos SSI-CEB o EEB proporcionan más capas y trazas para topologías de memoria de múltiples sockets o de alto canal.

La apariencia externa—cubiertas RGB y escudos decorativos—oculta un propósito funcional: un flujo de aire controlado y blindaje para regiones densas de alta velocidad. El firmware se convirtió en el orquestador que hace que los estándares heterogéneos se comporten de manera coherente. UEFI reemplazó al BIOS tradicional, habilitando la inicialización compleja para la ecualización de PCIe, el entrenamiento de DDR5, la política de USB4 y características de seguridad como Secure Boot y TPM 2.0 o TPM de firmware. El microcódigo de la plataforma y los marcos de los proveedores, como AGESA de AMD y el código de referencia de Intel, ofrecen mejoras continuas en la compatibilidad de memoria, el comportamiento de aumento y la enumeración de dispositivos, extendiendo la vida útil de una placa a lo largo de las actualizaciones de CPU y periféricos.

Las opciones para entusiastas como la bifurcación de carriles PCIe, Resizable BAR y ajuste de ASPM exponen los compromisos entre rendimiento, compatibilidad y potencia. En los servidores, un BMC dedicado con estándares como IPMI y Redfish añade gestión remota, telemetría y actualizaciones de campo independientes del CPU anfitrión. La integración a través de tantos dominios forzó nuevas prácticas de validación. Las placas se someten a pruebas de cumplimiento para diagramas de ojo de PCIe 5.0 y márgenes de receptor, entrenamiento de enlaces USB4 e interoperabilidad, y temporización de DDR5 a velocidades nominales, a menudo iterando el firmware para resolver casos especiales descubiertos con dispositivos de venta al por menor.

Las pruebas de compatibilidad electromagnética y coexistencia aseguran que los carriles de alta velocidad no interfieran con módulos inalámbricos o rutas de audio sensibles, mientras que las cámaras térmicas y las pruebas de transitorios de potencia verifican el comportamiento bajo aumentos de peor caso definidos por la gestión de potencia de los CPUs modernos. Las listas de proveedores calificados, las actualizaciones públicas de BIOS y los mapas de carriles claros en los manuales son el resultado visible de este trabajo, ayudando a los usuarios a navegar compromisos como deshabilitar puertos SATA cuando ciertos slots M.2 están ocupados. Por lo tanto, la placa base moderna es el respaldo silencioso que reconcilia la señalización de vanguardia con una compatibilidad retro pragmática. Soporta PCIe 5.0 a 32 GT/s junto a túneles USB4, alimenta cargas de cientos de vatios sin caída de voltaje y aún ofrece encabezados para periféricos más antiguos.

A medida que PCIe 6.0 con señalización PAM4 y corrección de errores hacia adelante llega a plataformas convencionales tras la adopción inicial en servidores, las placas ajustarán aún más sus presupuestos de señal y dependerán más de retimers y materiales de baja pérdida. Al mismo tiempo, la continua integración de CPUs desplazará algunas funciones de la placa, pero el trabajo seguirá siendo el mismo: asignar carriles, potencia y térmicas finitos para que los estándares dispares se sientan sin problemas para el usuario.