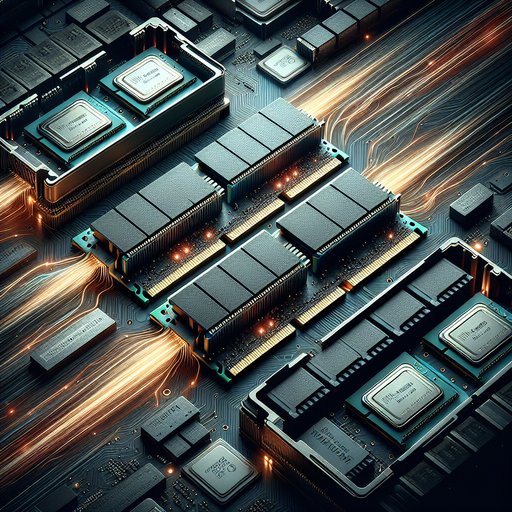

Hoofdgeheugen bevindt zich op een cruciaal knooppunt in elk computersysteem, waar snelle CPU's en versnellers worden verbonden met veel tragere opslag. De ontwikkeling van DDR4 naar DDR5 en de verkenning van opslagklasse-geheugens zoals 3D XPoint laten zien hoe ontwerpers streven naar meer bandbreedte en capaciteit, terwijl ze hardnekkige latentiegrenzen beheren. Naarmate het aantal kernen toeneemt, geïntegreerde GPU's in opkomst zijn en datarijke werkbelastingen groeien, wordt het verschil tussen een systeem dat zijn uitvoerende eenheden van stroom voorziet en een systeem dat vastloopt vaak bepaald door hoe het geheugen zich onder druk gedraagt. Begrijpen wat er veranderd is in de DDR-generaties en hoe de opkomende niveaus passen tussen DRAM en NAND, verduidelijkt waarom sommige toepassingen soepel opschalen terwijl andere plafonds bereiken lang voordat de CPU geen rekenkracht meer heeft.

Geheugen is cruciaal omdat de prestaties vaak niet worden beperkt door de rekencapaciteit, maar door hoe snel gegevens naar de rekeneenheden kunnen worden geleverd. De constante toename van CPU-parallelisme en vectorbreedte in de industrie heeft de vraag naar gelijktijdige, hoge-bandbreedte geheugentransacties vergroot. Ondertussen hielden de fysieke beperkingen van DRAM-cellen de fundamentele toegangslatentie in nanoseconden min of meer constant over generaties, wat een spanning creëert die architecten oplossen met meer kanalen, diepere wachtrijen en slimmere planningssystemen. De overgang van DDR4 naar DDR5 kan het beste worden gezien als een reactie op deze onbalans, in plaats van als een simpele snelheidsverhoging.

DDR4 legde de basis voor moderne platforms met datasnelheden die gewoonlijk variëren van 2133 tot 3200 mega-transfers per seconde en een 64-bits kanaal per DIMM. Groepen van banken en per-bank vernieuwing, geïntroduceerd en verfijnd in DDR3/DDR4, verbeterden de gelijktijdigheid door meerdere bewerkingen met minder conflicten te laten verlopen. Tegelijkertijd bleven de typische absolute toegangslatenties voor willekeurige leessessies rond de tientallen nanoseconden hangen, wat betekent dat software vooral prestatieverbeteringen opmerkte wanneer het parallelisme of de localiteit verbeterde. Terwijl servers overgingen van vier naar zes tot acht geheugenkanalen per socket, schaalde de totale bandbreedte om gelijke tred te houden met multi-core processors, zelfs als de latentie voor enkele toegang bijna onveranderd bleef.

DDR5 verhoogt de hoofdbandbreedte opzettelijk, met JEDEC-standaard datasnelheden die beginnen bij 4800 MT/s en verder stijgen tot meer dan 6400 MT/s naarmate de platforms zich ontwikkelen. Elke UDIMM is verdeeld in twee onafhankelijke 32-bits subkanalen, wat de efficiëntie van opdrachten verhoogt en de verspilling van bus tijd vermindert bij het overdragen van kleine datastromen. De burstlengte is verdubbeld naar 16 en het aantal bankgroepen is toegenomen, waardoor de pool van open pagina's en kansen voor de controller om rond conflicten te plannen is uitgebreid. On-module vermogensbeheer via een PMIC en de toevoeging van on-die ECC voor celbetrouwbaarheid verbeteren de signaalintegriteit en opbrengst zonder de noodzakelijke end-to-end ECC te vervangen.

Ondanks de sprong in bandbreedte verlaagt DDR5 niet magisch de werkelijke latentie; in feite hebben vroege modules vaak hogere cyclustellingen voor timing, en de absolute nanoseconde latentie kan vergelijkbaar zijn of iets slechter dan snel DDR4. Een eenvoudige vergelijking maakt het punt duidelijk: DDR4-3200 met CL16 levert ongeveer 10 ns CAS-latentie op, terwijl DDR5-6000 met CL36 rond de 12 ns zit, zonder tRCD en tRP in overweging te nemen. Moderne geheugencontrollers verhelpen dit door geheugenniveau-parallelisme te extraheren, waardoor veel verzoeken simultaan kunnen worden verwerkt en de uitgebreide bankstructuur kan worden benut om individuele toegangvertragingen te verbergen. Werkbelastingen die gelijktijdige stromen kunnen genereren, zoals geïntegreerde grafische kaarten of grote gegevensscans, profiteren enorm van de bandbreedte van DDR5, zelfs als de latentie van de eerste byte onveranderd blijft.

Serverplatforms versterken deze effecten door DDR5 te combineren met meer geheugenkanalen en DIMMs met een hogere capaciteit, wat zowel de bandbreedte als de voetafdruk voor in-geheugen datasets vergroot. Nieuwere CPU's bieden acht of meer DDR5-kanalen per socket, en gestapelde chiptechnieken verhogen de capaciteiten per DIMM, zodat databases, analysekaders en virtualisatiehosts meer actuele gegevens dicht bij de rekeneenheid kunnen houden. Verbeterde vermogenslevering op de DIMM helpt de signaalintegriteit op hogere snelheden te behouden, wat cruciaal is in dichtbevolkte serverborden. Het eindresultaat is een hogere duurzame doorvoer voor geheugengevoelige, parallelle werkbelastingen, terwijl single-threaded, willekeurig toegankelijke code bescheiden verbeteringen ziet, tenzij de software de localiteit en de mogelijkheid tot prefetching verbetert.

3D XPoint, commercieel gemaakt door Intel als Optane, toonde een aanvullend pad door een persistente, byte-adresseerbare laag tussen DRAM en NAND in te voegen. In DIMM-vorm waren de leellatenties enkele keren hoger dan die van DRAM maar ver onder die van NAND, en in NVMe-vorm leverde het toegangstijden in enkele microseconden, wat dramatisch sneller was dan typische SSD's. Datacenterimplementaties gebruikten het om het geheugen economisch uit te breiden en om metadata, indexen en schrijfintensievere logboeken te versnellen via een hogere duurzaamheid dan NAND. Hoewel zowel Intel als Micron de productie van 3D XPoint in 2022 stopzetten, valideerde het gebruik in de praktijk geheugenlagen: het plaatsen van grote, iets langzamere media dicht bij de CPU vermindert de druk op DRAM, vermindert I/O-versterking en verbetert de staartlatenties voor datagevoelige diensten.

De praktische impact van bandbreedte en latentie varieert met de kenmerken van de werkbelasting. Geïntegreerde GPU's schalen bijna lineair met geheugenbandbreedte omdat ze geen toegewijde VRAM hebben, waardoor de hogere doorvoer van DDR5 vooral waardevol is voor gamen op iGPU's en voor GPU-achtige berekeningen op APU's. AI-inferentie met grote embeddings, in-geheugen analyses en graf traversals profiteren wanneer veel uitstaande verzoeken kunnen worden overlapt, terwijl takken- en pointer-jachtcode die prefetchers omzeilt, latentiegebonden blijft. Ontwikkelaars zien het verschil in profiling: geheugenstops verminderen wanneer er gelijktijdigheid en streamingpatronen aanwezig zijn, terwijl pointer-wandelingen met één baan beperkt blijven door de nanoseconden van de eerste toegang.

Vooruitkijkend blijft de hiërarchie zich verbreden: HBM gekoppeld aan versnellers levert honderden gigabytes per seconde per stap voor massaal parallelle kernels, terwijl DDR5 algemene rekencapaciteit met brede capaciteit en kostenefficiëntie verankert. Coherente interconnecties zoals CXL voegen nieuwe manieren toe om uitgebreid geheugen aan te sluiten met iets hogere latenties, waardoor pooling en layering mogelijk zijn zonder applicaties opnieuw te platformen. Deze trends verschuiven prestatie-engineering naar topologie-bewuste allocatie, NUMA-bewuste gegevensplaatsing en algoritmen die aaneengeschakelde, parallelle toegang maximaliseren. De winnaars zijn systemen die geheugen niet als een monolith beschouwen, maar als een set lagen, elk optimaal benut voor wat het het beste doet.

De rode draad van DDR4 naar DDR5 en door opslagklasse-geheugen is duidelijk: bandbreedte en parallelisme schalen agressief, terwijl de intrinsieke DRAM-latentie langzaam beweegt. Hardware reageert met meer kanalen, banken, subkanalen en slimmere controllers; software reageert met gegevensindelingen en toegangspatronen die die structuur omzetten in nuttig werk. Door werkbelastingen te koppelen aan de juiste laag—snelle DRAM voor hete, willekeurige gegevens; hoge-bandbreedte DDR5 voor parallelle stromen; persistente geheugen voor capaciteit-dicht bij caching—kunnen architecten potentiële knelpunten omzetten in doorvoer. De evolutie draait minder om het najagen van een enkele maatstaf en meer om het in balans houden van de gehele pijplijn, zodat rekencapaciteit, geheugen en opslag dezelfde richting op trekken.